- #MODELSIM SIMULATION MANUAL#

- #MODELSIM SIMULATION PRO#

- #MODELSIM SIMULATION SOFTWARE#

- #MODELSIM SIMULATION CODE#

#MODELSIM SIMULATION SOFTWARE#

#MODELSIM SIMULATION CODE#

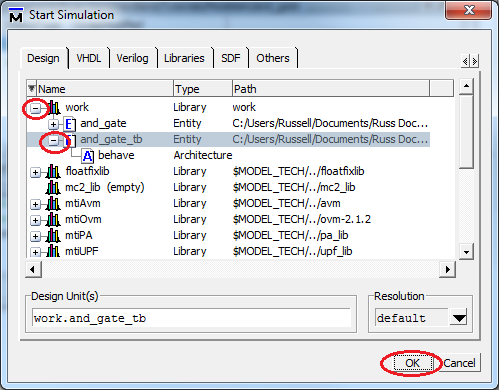

Modelsim is a powerful tool used to simulate Verilog or VHDL code that you have written. The Quick and Dirty Guide to Using ModelSim with Quartus - Julie Wang 2014

# "eval vcom $USER_DEFINED_VHDL_COMPILE_OPTIONS $USER_DEFINED_COMPILE_OPTIONS "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_syn_attributes.vhd".

# "vcom C:/intelfpga_pro/18.0/quartus//eda/sim_lib/altera_syn_attributes.vhd -work altera" novopt option is now deprecated and will be removed in future releases.

#MODELSIM SIMULATION MANUAL#

If you are using this switch to preserve visibility for Debug or PLI features, please see the User's Manual section on Preserving Object Visibility with vopt. This will cause your simulation to run very slowly. # ** Error (suppressible): (vcom-12110) All optimizations are disabled because the -novopt option is in effect. # Model Technology ModelSim SE-64 vcom 10.7 Compiler 2017.12 Dec 7 2017 Run 2 if I change VoptFlow to 0 I get an error when runing: Vcom -O0 -work work $QSRC_DIR/HwSrc/UT_DP_PreProc.vhdĪdd wave -noupdate -group DP_C sim:/compactor_tb/CompactorDUT/CompBasic/DP_C/* Vcom -O0 -work work $QSRC_DIR/HwSrc/UT_DataProcessing.vhd Vcom -O0 -work work $QSRC_DIR/HwSrc/UTDataProcSimTop.vhd Vcom -work work $QPRJ_DIR/TestBenchs/UTDPtestBench.vhd Source $QSYS_SIMDIR/mentor/msim_setup.tcl Thanks, set QPRJ_DIR D:/LHCb/FPGAPrjs/UTDataProcV01 So, what I'm doing wrong? what would be the correct set of options in order that Modelsim shows all signals including the ones for debug? I attach the simScript.do where now is the -O0 option I'v tried multiple options from vopt but without success.

#MODELSIM SIMULATION PRO#

I'm simulating with modelsim 10.7 a design created with Quartus Prime Pro 18, but I don't know hot to do the simulation with no optimizations with this new version.

0 kommentar(er)

0 kommentar(er)